L’indispensable concorde numérique : Serveurs et processeurs

Jan 2023Par Frédéric Bergonzoli

En matière d’avancées dans le domaine des processeurs, 2023 sera un bon cru. Les fondeurs AMD, Intel et Nvidia ont annoncé le renouvellement de leurs offres et, avec elles, la perspective de doper l’accélération des traitements des gigantesques volumes de données et autres calculs en temps réel. Toutes choses que les applications ne cessent de solliciter dans tous les secteurs.

Les premières machines à bénéficier des nouvelles puces seront disponibles à grande échelle cette année. Parmi elles, les serveurs, porte-étendards technologiques qui abritent dans leurs entrailles ce que l’IT fait de mieux, ainsi que les capacités de support des charges de travail, tous dépassent de loin ce que peut délivrer le commun des ordinateurs de bureau.

Les processeurs des serveurs diffèrent de ceux des PC, d’abord par la plate-forme sur laquelle ils reposent. Chez AMD, les puces Ryzen des desktops ne pourraient remplacer les processeurs Epyc destinés aux serveurs, pas plus que chez Intel, les Core pourraient se substituer aux Xeon.

Autre distinction significative, les processeurs de bureau présentent des vitesses d’horloge plus élevées. Voilà qui est idéal pour répondre aux charges de travail à thread unique d’applications comme la bureautique, la conception graphique ou encore le montage vidéo. En outre, les puces des PC peuvent disposer d’un surplus de performances, grâce notamment à l’overclocking, mais chauffent alors plus rapidement. C’est pourquoi les fabricants de PC conçoivent des machines aux espaces ventilés et ne lésinent pas sur le système de refroidissement. Au prix d’une consommation d’énergie accrue, ils n’ont pas à se soucier de la surchauffe du processeur embarqué.

« Processeur tout-terrain, le Xeon est conçu pour servir les besoins en HPC et les tâches quotidiennes »

Mickael Moreau, responsable de la communication d’Intel France

Divergence d’objectifs

Les enjeux ne sont pas les mêmes pour les serveurs. Dans les data centers, même si les méthodes de refroidissement sont satisfaisantes, la multiplication d’équipements dans un espace réduit constitue un défi pour contenir les émissions de calories. D’autant plus que les processeurs dédiés aux serveurs s’appuient sur un nombre croissant de cœurs, de sorte qu’il leur est nécessaire d’adopter des vitesses d’horloge inférieures.

Pourquoi ? Non seulement pour maintenir de la température sous son seuil critique, mais aussi pour assurer un fonctionnement stable en 24/7.

Ces différences de conception en fonction deux grands usages ne freinent pas les évolutions propres aux technologies des processeurs, dont la loi de Moore est l’une des modélisations. Alors qu’Intel cherche à fabriquer des puces abritant plus d’un milliard de transistors d’ici à 2030, les architectures de processeurs profitent du rythme régulier des améliorations générationnelles.

Les limites du CPU face aux exigences du traitement parallèle massif a ainsi favorisé le développement du GPU, puis du DPU (data processing unit) pour le calcul massif de données volumineuses en un temps court avec, en filigrane, la nécessité d’optimiser la transmission des données entre la mémoire et le processeur.

Si GPU et DPU s’articulent autour de l’unité centrale pour accélérer les traitements, la voracité en ressources d’applications, comme l’I.A., exige que le système soit souple : cette spécialisation des composants autour du CPU entraîne une « désagrégation » d’autres éléments des serveurs comme la mémoire, les cartes réseaux ou le stockage, dont la gestion est déportée des processeurs centraux. C’est précisément l’objectif atteint par une nouvelle génération de serveurs s’appuyant sur le protocole CXL (compute express link), qui facilite le partage des ressources dans des architectures dites composables.

En outre, les nouveaux processeurs du marché supportent ce protocole, outre la mémoire DDR5 et le bus PCIe 5.0. De quoi bâtir des serveurs qui tirent parti des accélérateurs GPU et DPU, et de l’autonomie des composants de la carte mère. Les fabricants s’appuient sur les approches respectives des fondeurs.

Chez Intel, le SoC accueille de nouveaux moteurs d’accélération. « Le Xeon est un processeur tout-terrain conçu pour servir à la fois les tâches quotidiennes d’une entreprise et les besoins en calcul haute performance. Sa quatrième génération, Sapphire Rapids intègre quatre accélérateurs qu’il faut voir comme des composants spécialisés au sein du composant générique. Le premier, AMX (Advanced Matrix Extension), vise à accélérer les calculs d’intelligence artificielle ; le second, DSA (Data Streaming Accelerator) est dédié à la protection du stockage ; le troisième, IAA (In-Memory Analytics), accélère les traitements liés aux bases de données ; le dernier, QAT (QuickAssist Technology), accélère ce qui concerne la compression et décompression tout comme la cryptographie, en particulier dans les domaines de la vidéo et de la sécurité », détaille Mickael Moreau, responsable de la communication d’Intel France.

Hasard du calendrier, AMD annonce la quatrième génération de ses processeurs Epyc. Nommée Genoa, la première version de la nouvelle famille embarque « jusqu’à 96 cœurs dans un seul processeur grâce auxquels on déploie des serveurs moins nombreux et plus puissants, en offrant jusqu’à 2,8 fois plus de performances que la concurrence, tout en diminuant sa consommation d’énergie de 54 % », souligne le fabricant. Ces puces performantes et écologiques devraient elles aussi façonner le marché des serveurs.

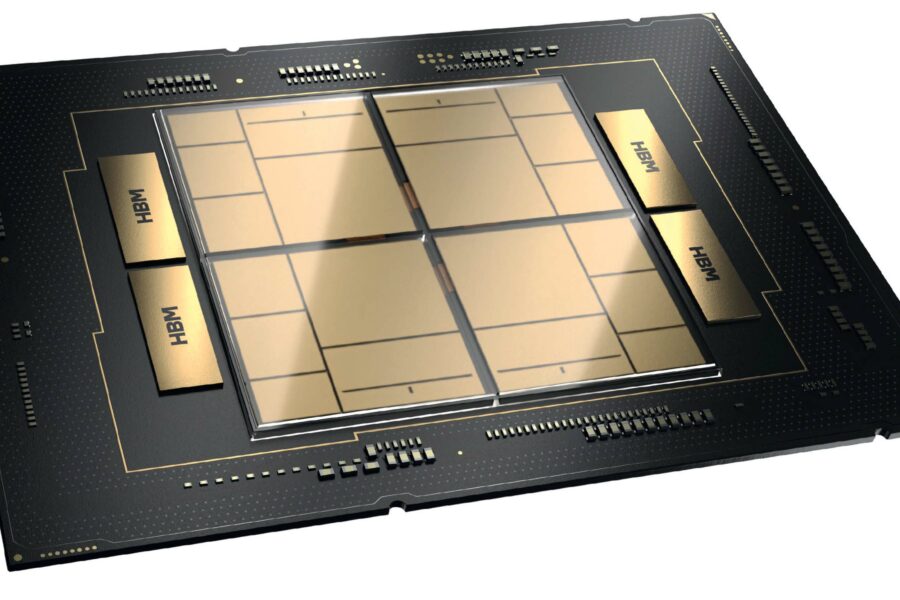

Du côté de Nvidia, ce sont les processeurs Grace qui sont mis en avant pour assurer les traitements massifs d’I.A. et de HPC, ou encore pour alimenter les systèmes de recommandation. Deux versions seront disponibles courant 2023. La première se nomme Grace Superchip. « Elle combine deux ARM placés sur la même carte porteuse pour un total de 144 cœurs dotés du jeu d’instruction Neoverse V2 et une nouvelle interface cohérente à 900 Go/s, soit sept fois plus rapide que la norme PCIe Gen 5 », indique de son côté Jean-Charles Vasnier, Senior Solutions Architecte chez Nvidia. La seconde mouture est baptisée Grace Hopper. « Elle comprend un CPU Grace 72 cœurs et un GPU Hopper de type H100. »

« Grace Superchip et Grace Hopper assurent les traitements massifs d’I.A. et de HPC, ou alimentent les systèmes de recommandation »

Jean-Charles Vasnier, Senior Solutions Architect, Nvidia

Le protocole CXL s’accapare le futur immédiat

La généralisation du protocole CXL (compute express link) est renforcée par la venue des processeurs Intel Xeon Sapphire Rapids et AMD Epyc Genoa. Les deux puces concurrentes supportent ce protocole opérant sur un bus PCIe 5.0 (CXL 1.1), dont l’intérêt est de faciliter la conception de systèmes de ressources partagées sur un réseau avec une faible latence et un haut débit. Qu’il s’agisse de mémoire, GPU, DPU sous forme de carte réseau (SmartNIC) ou encore de FPGA, CXL accélère les échanges au sein d’un serveur en jouant le rôle d’une super-extension du bus PCIe.

Autre intérêt, les ressources sont partageables entre serveurs – CXL peut, par exemple, utiliser la mémoire ou les GPU de plusieurs systèmes plutôt que d’un seul. Et surtout, servir les architectures de désagrégation des serveurs qui décomposent les éléments des systèmes en parties auto-opérationnelles et connectées par réseau, et non plus par soudures ou interfaces. Amorcé par Intel, le CXL est soutenu par un consortium qui regroupe une majorité de fondeurs, fabricants et hyperscalers.

Intel veut placer un billion de transistors sur ses puces

Le fondeur veut faire mentir les prédictions du déclin de la loi de Moore, selon laquelle le nombre de transistors incorporés sur une puce de circuits intégrés double environ tous les deux ans. Intel a annoncé « des avancées en matière de recherche qui alimentent son pipeline d’innovation pour maintenir la loi de Moore sur la voie d’un milliard de transistors sur une solution, et ce dans la prochaine décennie ».

Ses laboratoires voient notamment dans le packaging 3D la possibilité d’« améliorer la densité par un facteur dix ; de nouveaux matériaux pour la mise à l’échelle des transistors 2D au-delà du RibbonFET, de nouvelles possibilités en matière d’efficacité énergétique et de mémoire pour une informatique plus performante, et des avancées pour l’informatique quantique ». Soixante-quinze ans après l’invention du transistor, le fabricant américain veut tout simplement parvenir à en placer 1 000 milliards sur un nouveau matériau de seulement trois atomes d’épaisseur. Microns, nanomètres puis angströms : la porte vers la miniaturisation est loin d’être fermée.