Des SmartNIC pour alléger les unités centrales

Comment optimiser les performances des serveurs dans les data centers ? En exploitant les SmartNIC, ces cartes réseaux intelligentes qui embarquent des processeurs dédiés capables de décharger les CPU centraux de diverses tâches.

Déc 2022Par Benoît Huet

Les opérateurs, les services providers et les entreprises utilisatrices cherchent des solutions pour rendre leurs data centers plus économiques, plus écologiques et plus performants. Et l’une des grandes tendances qui y participe est l’emploi massif d’accélérateurs de type SmartNIC DPU (data processing unit), permettant de décharger les traitements des processeurs centraux sur plusieurs tâches : mise en réseau, stockage, sécurité et même l’hyperviseur pour séparer davantage la couche de gestion de l’infrastructure du reste du serveur.

En clair, il est plus opportun de conserver la virtualisation du calcul sur le CPU du serveur, et confier les fonctions entrée sortie au niveau du réseau, du stockage et de la sécurité à une DPU ou à des processeurs dédiés (comme les infrastructure processing units chez Intel) embarqués sur la SmartNIC, une carte accélératrice réseau intelligente. Les applications maximiseront ainsi leur utilisation de la bande passante disponible, et offriront leurs meilleures performances. En outre, les SmartNIC répondront à des usages autour des télécommunications : par exemple, avec l’avènement de la 5G, certaines DPU embarquées sur les SmartNIC prennent en charge les systèmes Open RAN (lire l’E.D.I n° 122, p.130) permettant de déployer cette 5G et d’en assurer l’interconnectivité ou l’interopérabilité à très grande échelle.

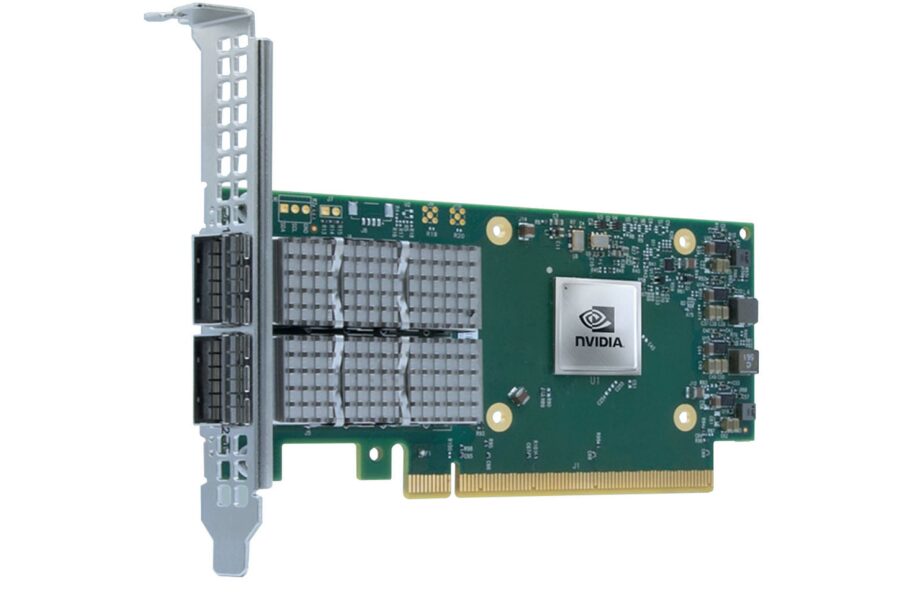

Une SmartNIC est une carte accélératrice réseau intelligente grâce à laquelle les applications maximisent leur utilisation de bande passante, et optimisent leurs performances.

Bataille d’architectures

Techniquement, une SmartNIC peut être basée sur des architectures : Asic (application specific integrated circuit), FPGA (field-programmable gate array), MPPA (matrice de processeurs massivement parallèles) ou Soc. Déjà, l’avantage de l’Asic est sa réponse optimale au besoin à réaliser. Ainsi, elle consomme moins d’énergie et sa personnalisation lui confère une sécurité accrue. Mais elle n’offre pas, notamment pour certains spécialistes, une programmabilité suffisante. Ensuite, l’architecture FPGA, elle, est programmable et reprogrammable ; elle offre des temps de latence faibles, d’où leur intérêt croissant dans le monde de l’IoT et la 5G. Reste que les FPGA demeurent encore complexes à programmer et sont plus coûteuses.

Une alternative intéressante pour l’informatique reconfigurable – moins énergivore et plus facile à programmer – est l’usage des MPPA. C’est la voie notamment empruntée par Kalray pour son DPU Coolidge. C’est une architecture capable de traiter les données en temps réel, et de programmer simplement tous les traitements. Enfin, pour diminuer le nombre de composants et celui des interconnexions – donc les coûts –, certains acteurs comme Microsemi, Xilinx (AMD) ou Intel, proposent des FPGA sur SoC, c’est-à-dire des dispositifs qui combinent une structure programmable FPGA couplée à un ou plusieurs processeurs embarqués.

les principaux fondeurs se partagent le segment

A noter que ce juteux marché est principalement dominé par les grands fondeurs de CPU et GPU comme Nvidia, Intel, AMD qui ont massivement investi en interne ou par des rachats d’entreprises. Exemples : Nvidia avec le rachat de Mellanox en 2020 ; AMD qui a procédé aux acquisitions successives de Xilinx en 2020, puis de Pensando en 2022 ; ou encore Intel qui s’était offert Altera en 2015. Face à ces grands acteurs, figurent aussi des challengers comme l’américain Fungible ou le français Kalray. à l’origine, ce sont surtout Amazon (notamment via Annapurna Labs avec Nitro) et Microsoft (dès 2015, par l’implémentation des SmartNIC Azure AccelNet dans les serveurs du groupe) pour leurs besoins internes qui ont véritablement propulsé le marché des SmartNIC.